Глава 1. Системы памяти

Содержание

Эта глава содержит некоторые понятия и технологии, применяемые для действенного управления данными в памяти, включая иерархию памяти, архитектуру доступа к неоднородной памяти (NUMA, non-uniform memory access) и энергонезависимой памяти с произвольным доступом (NVRAM, non-volatile random access memory). Это те основы, на которые существенным образом полагается производительность систем управления данными В памяти (In-Memory).

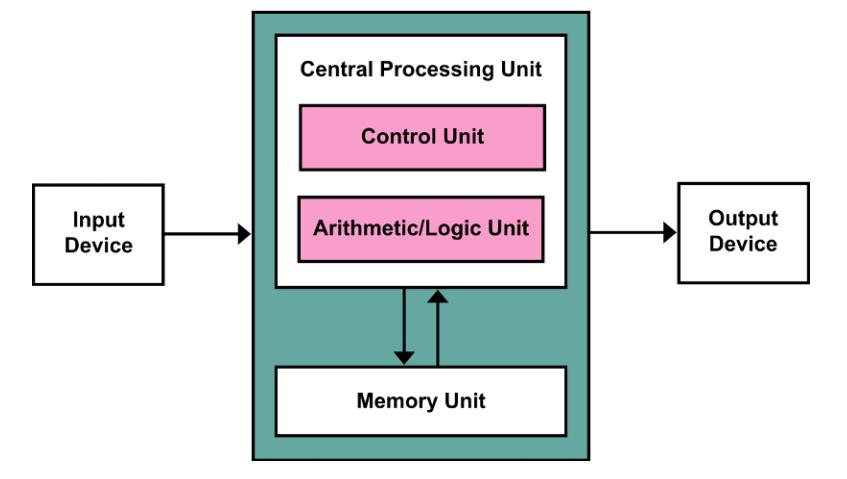

Память играет значительную роль в вычислительной архитектуре фон Неймана, отображённой на Рисунке 1.1. Это часть всей вычислительной системы, применяемая для хранения как данных смой программы, так и инструкций этой программы.

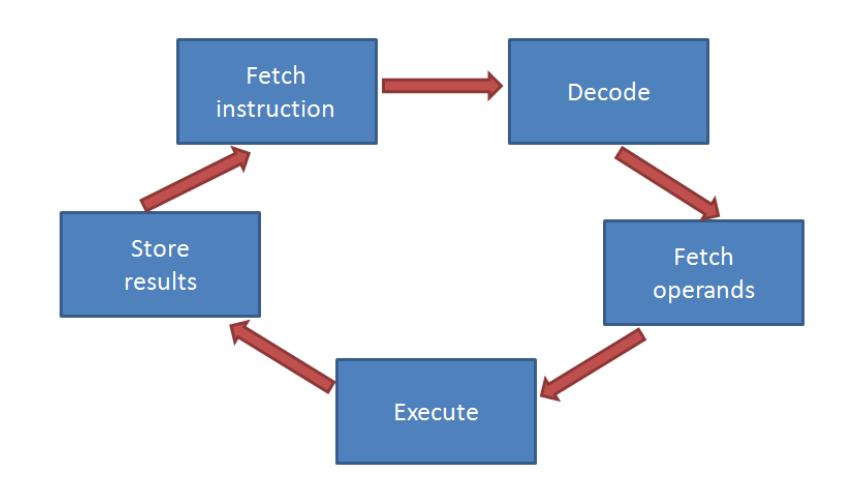

Типичный цикл выполнения инструкций архитектуры ЦПУ фон Неймана обычно состоит из следующих пяти шагов [1]:

-

Выборка одной инструкции из памяти

-

Декодирование этой инструкции

-

Выборка необходимых операндов данной инструкции из памяти, в случае необходимости

-

Выполнение

-

Сохранение полученного результата данной инструкции в памяти, в случае необходимости

На протяжении цикла с Рисунка 1.2, наша система памяти получает доступ по крайней мере один раз (на шаге 1); однако, в зависимости от своей исполняемой инструкции она может применяться множество раз. Частый доступ это одна из основных причин по которой такая система памяти жизненно важная часть всей системы и чувствительный элемент производительности вычислительной системы в целом.

Память составлена из большого массива байт [1]. Всякий Байт это соответствующий массив, обладающий двумя основными характеристиками:

-

Неким адресом

-

Каждый элемент (адрес) может быть доступен независимо от прочих

Единственной обязанностью памяти является хранение или извлечение информации по указанным адресам. С точки зрения памяти единственным входом выступает поток адресов и управляющее слово, указывающее нужно ли считывать, или записывать информацию по соответствующему адресу. То, как сама программа вырабатывает эти адреса не существенно: они могут поступать из счётчика своей программы, массива с индексами, непосредственно, по реальному адресу, помимо прочего. Эта информация не относится к делу. Само ожидаемое от памяти системой поведение то же самое: выборка той информации, которая хранится по заданному адресу.

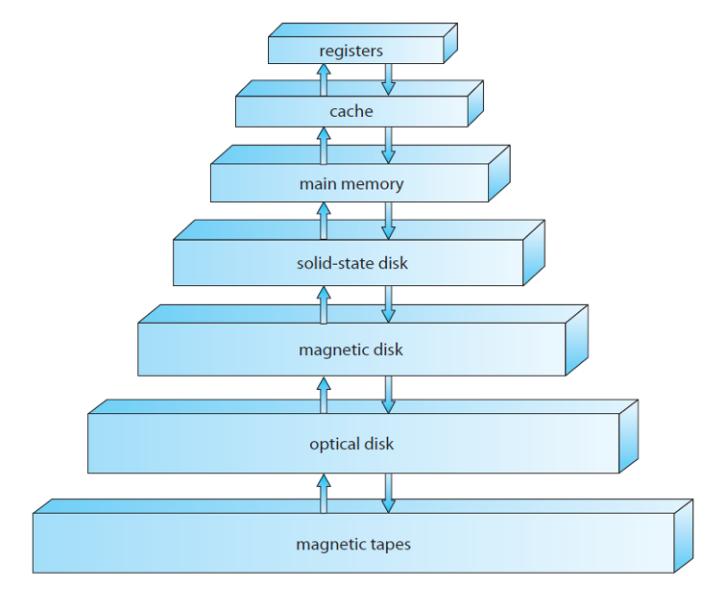

Имеющаяся иерархия памяти определяется в терминах задержки доступа и величины логического расстояния от её ЦПУ. В целом, она состоит из регистров, кэша, основной памяти и дисков; от наивысшей производительности до наинизшей.

Рисунок 1.3 отображает иерархию типичной организации памяти. Она показывает, что доступ к данным на более верхних уровнях намного быстрее чем на нижних, причём каждый из этих уровней будет представлен в этом разделе.

В современных архитектурах данные не могут обрабатываться ЦПУ пока они не помещены в регистры. Таким образом, подлежащие обработке данные обязаны передаваться по всем уровням памяти пока они не достигнут регистров. Следовательно, каждый более верхний уровень служит в роли кэша лежащему ниже уровню для снижения значения задержки при повторяющемся доступе к данным.

Иерархия памяти состоит из множества уровней, однако данные могут копироваться за раз только между двумя соприкасающимися уровнями [2]. Самый верхний уровень это самый ближний к своему процессору и он меньше и более быстрый чем лежащий ниже, так как более верхний уровень пользуется более затратной технологией.

Минимальный элемент сведений, который может быть представлен или не представлен в соответствующей иерархии двух уровней носит название блока или строки (line). Когда некие запрашиваемые своим процессором данные присутствуют в неком блоке на самом верхнем уровне это носит название попадания (hit). Если данные не найдены на самом верхнем уровне, такой запрос носит название промаха (miss). Тогда выполняется доступ к более нижнему уровню в имеющейся иерархии для выборки запрашиваемого блока данных. Значение скорости попадания, или соотношение попаданий это значение части доступа к памяти, найденной на самом верхнем уровне; оно часто применяется как мера значения производительности в имеющейся иерархии памяти. Величина скорости промахов это та часть доступа к памяти, которая не обнаружена на самом верхнем уровне.

Значение производительности программы, интенсивно использующей данные, в сильной степени зависит от загруженности имеющейся иерархии памяти [2]. Как достичь хорошей пространственной и временной локальности обычно имеет наибольшее значение для оптимизации эффективности. В частности, пространственная локальность предполагает, что доступ к смежным данным с большей вероятностью будет осуществляться совместно, в то время как временная локальность относится к наблюдению за вероятностью повторного доступа к элементу в ближайшем будущем. Производительность выступает основной причиной наличия иерархии памяти, поэтому важно значение времени на обслуживание попаданий и промахов. Время попадания это время доступа к верхнему уровню иерархии памяти, которое содержит время, необходимое для определения того, является ли доступ попаданием или промахом. Штраф за промах это время замены блока верхнего уровня соответствующим блоком нижнего уровня плюс время доставки этого блока самому процессору. Поскольку верхний уровень меньше и построен с применением более быстрых составляющих памяти, время попадания будет намного меньше чем время доступа к следующему уровню в иерархии, что и составляет основной компонент штрафа за промах.

Применяемые при построении систем памяти понятия воздействуют на многие прочие стороны компьютера, включая и то как его операционная система управляет памятью и вводам/ выводом, как компиляторы вырабатывают код и даже как приложения пользуются самим компьютером [5].

Существует ряд первейших технологий памяти, применяемых в наши дни в современной вычислительной системе [2]:

-

Регистр

-

Кэш

-

SRAM: Static Random-Access Memory - Статическая память с произвольной выборкой

-

DRAM: Dynamic Random-Access Memory - Динамическая память с произвольной выборкой

-

Флэш память (электрически перепрограммируемое устройство)

-

NVM: Non-Volatile Memory - энергонезависимая память

-

Магнитные хранилища

Каждая категория памяти обладает собственными требованиями и способна реализовываться с применением различных физических технологий. Данная классификация памяти представляет некую абстракцию технологий памяти. {Прим. пер.: подробнее в нашем переводе Высокопроизводительные вычисления Больших данных Дхабалешвар К. Панда, Сяойи Лу и Дипти Шанкар, Copyright © 2022 assachusetts Institute of Technology.}

Основная память (SRAM, DRAM, NVM) также носит название внутренней памяти, к которой может выполняться непосредственный доступ и возможен доступ ЦПУ, в противоположность внешним устройствам, таким как диски.

Регистр процессора это небольшой объём хранения внутри ЦПУ, с которым способны непосредственно манипулировать инструкции. В обычной инструкции данные сначала загружаются из лежащих ниже уровней памяти в регистры, где они применяются для арифметических или проверочных операций, а получаемый результат получается обратно в другой регистр, который зачастую затем обычно сохраняется обратно в основную память либо последующей инструкцией, либо чем- то ещё впоследствии. Значение длины регистра обычно равна длине слова ЦПУ, однако также существуют слова двойной длины и ещё более широкие регистры (например, регистры YMMX шириной 256 бит в микроархитектуре ЦПУ Intel Sandy Bridge), которые могут применяться в одной инструкции операций со множеством данных (SIMD, single instruction multiple data). Хотя значение числа регистров и зависит от конкретной архитектуры, общая ёмкость регистров намного меньше чем лежащий ниже уровень, например, кэш памяти. Однако, доступ к данным из регистров намного быстрее.

Современные процессоры способны выполнять инструкции со скоростью одной или более инструкций за такт ЦПУ, а регистры внутри самого процессора доступны по именам внутри одного такта ЦПУ. К сожалению, завершение доступа считывания или записи памяти может потребовать много циклов ЦПУ и обычно процессору приходится приостанавливаться. Основная память и встроенные в сам ЦПУ регистры представляют собой хранилище общего назначения, к которому это ЦПУ способно обращаться напрямую. Таким образом, любая подлежащая исполнению инструкция и все требуемые этой инструкцией данные должны присутствовать в одном из этих устройств хранения с прямым доступом. Они должны быть на месте прежде чем ЦПУ сможет с ними работать, в противном случае требуется перезапуск данной инструкции [2]. Обычным средством предотвращения зависания процессора является добавление быстрой памяти между самим ЦПУ и основной памятью, как правило, в самой микросхеме ЦПУ. Конкретно этот тип памяти носит название кэша. Попадание в кэш происходит когда инструкция или данные инструкции присутствуют в кэше когда они требуются своему процессору. В противном случае это кэш- промах. Существует ряд способов минимизации числа промахов кэша, которые будут рассмотрены в нашем следующем разделе.

Регистры играют роль контейнеров хранения, которые ЦПУ применяет для обработки инструкций, в то время как кэши действуют в качестве моста между такими регистрами и основной памятью по причине высокого значения задержки по перемещению между регистрами и основной памятью. Кэш создаётся на высокоскоростной статической памяти (SRAM) вместо более медленной и экономичной динамической памяти (DRAM), которая обычно формирует свою основную память. В целом, существуют три уровня кэша, а именно, кэш L1, кэш L2 и кэш L3 (также носящего название кэша последнего уровня - LLC, last level cache), причём с возрастанием задержки и ёмкости. L1 кэш далее подразделяется на кэш данных (то есть L1-dcache) и кэш инструкций (или L1-icache) во избежание взаимного влияния между доступом к данным и доступом к инструкциям.

Как правило, кэш подразделяется на строки (line) логического кэша фиксированной длины, которые выступают атомарными элементами для передачи данных между различными уровнями кэша и между последним уровнем кэша и основной памятью. В современных архитектурах строка кэша обычно обладает длиной в 64 байта. Заполняя кэши для каждой строки кэша для повышения производительности можно пользоваться пространственной локальностью. Отображение между основной памятью и кэшем определяется рядом стратегий, например, прямым соответствием, ассоциативным набором с N- путями и полностью ассоциативным. При непосредственном отображении каждая запись (строка кэша) в памяти может быть помещена лишь в одно место в кэше, что ускоряет процесс адресации. При полностью ассоциативной стратегии каждая запись может быть помещена в любое место, что обеспечивает меньшее число промахов кэша. N- ассоциативная стратегия предоставляет собой некий компромисс между непосредственным отображением и полностью ассоциативной: она позволяет каждой записи находиться в любом из N мест кэша, который носит название набора кэша. На практике часто применяется ассоциативность с N- путями, а соответствующее отображение предопределено с точки зрения наборов кэша.

Кроме того, в большинстве архитектур обычно применяется стратегия замены только что использованного (LRU, least recently used) для вытеснения строки кэша в случае нехватки мета. Такая схема, по существу, для повышения производительности применяет временную локальность. Задержка доступа к кэшу намного короче задержки доступа к основной памяти. С целью получения хорошей производительности ЦПУ нам необходимо гарантировать высокую скорость попадания в кэш для уменьшения числа обращений к памяти с высокой задержкой. При разработке системы управления обработки в памяти важно применять свойства пространственной и временной локальности кэшей. Например, было бы быстрее обращаться к памяти последовательно, нежели произвольным образом, а также лучше было бы хранить часто применяемые объекты в кэше. Преимущество последовательного доступа к памяти усиливается установленными в современных ЦПУ стратегиях предварительной выборки.

SRAM это тип памяти с произвольным доступом (RAM, random-access memory) в которой для хранения каждого бита используется схема фиксации (триггера - flip-flop). SRAM энергозависимая память; в случае отключения питания данные теряются. Термин "статическая" отличает SRAM от DRAM (динамической оперативной памяти), которая обязана периодически обновляться. SRAM быстрее и дороже нежели DRAM; обычно она применяется для кэша и внутренних регистров ЦПУ, а DRAM используется для основной памяти компьютера.

SRAM может быть встроена в качестве оперативной памяти или кэш- памяти в микроконтроллеры (как правило, от 32 байт до 128 килобайт) для хранения регистров и частей конечных автоматов, применяемых в некоторых микропроцессорах (смотри файл регистра), в прикладных ИС или ASIC (как правило, порядка килобайт), а также в программируемой пользователем вентильной матрицы и в устройстве сложной программируемой логики (Field Programmable Gate Array and Complex Programmable Logic Device).

SRAM предлагает простой доступ к данным и не требует циклов обновления. Её производительность и надёжность хороши, а энергопотребление в режиме ожидания низкое. Поскольку для реализации SRAM на один бит требуется больше транзисторов, она менее плотная и более дорогостоящая чем DRAM, а также обладает более высоким энергопотреблением при доступе на считывание и запись. Энергопотребление SRAM пребывает в широком диапазоне в зависимости от частоты обращения к ней.

Данная технология памяти ближе всего в ЦПУ, поскольку её время доступа наиболее близко к тактовой частоте ЦПУ. Она способна достигать такой производительности поскольку не требует обновления; к сожалению, эта технология затратна, поскольку применяет от шести до восьми транзисторов на бит [3].

Многие категории промышленных и научных подсистем, автомобильной электроники и аналогичных встраиваемых систем содержат SRAM, которая, в данном контексте может именоваться как ESRAM. Какое- то количество (килобайты или меньше) также встраиваются практически во все устройства, игрушки и тому подобное, во всё что реализует электронный интерфейс с пользователем. SRAM также применяется в персональных компьютерах, рабочих станциях, маршрутизаторах и в периферийном оборудовании: в файлах регистров ЦПУ, во внутреннем кэше ЦПУ и в кэшах SRAM режима внешнего взрывного роста, в буферах жёстких дисков, буферах маршрутизаторов и т.п. ЖК экраны и принтеры также обычно пользуются SRAM для удержания отображаемого изображения (или подлежащего печати).

Это также полупроводниковая память, в которой значение бита может сохраняться пока оно запитано. Для сохранения сведений о нём применяется заряд конденсатора; к сожалению, эту ёмкость необходимо периодически обновлять. DRAM применяет организацию со структурой двухуровневого декодирования. Такая схема делает возможным обновление всех строк целиком, а также увеличивает производительность, что достигается за счёт буферизации строк в SRAM вместо самой микросхемы [3].

К тому же DRAM обладает независимым таймером становясь асинхронной чтобы допускать:

-

Пакетную передачу битов без указания дополнительных битов адреса.

-

Более быстрая версия DRAM носит название SDRAM с двойной скоростью передачи (double data rate) или DDR SDRAM. Такое название подразумевает, что эта память способна передавать данные по переднему и по заднему фронту тактового сигнала, действенно удваивая тот объём информации, который способны производить её микросхемы.

Кроме того, для поддержания максимально возможных полос пропускания, разумно организовывать память на чтение и запись из множества банков памяти, каждый из которых обладает собственным SRAM буфером строк.

В последние годы DRAM становится не дорогой и достаточно ёмкой, что превращает базу данных в памяти в жизнеспособную.

Флэш память [2] это тип электрически стираемой программируемой памяти с доступом на чтение (EEPROM, electrically erasable programmable read-only memory).

Существует два основных вида флэш памяти: NOR флэш и NAND флэш, которые носят название по логическим затворам NOR и NAND. NOR и NAND флэш применяют ту же самую архитектуру ячеек, составляемую из плавающего затвора MOSFET. На уровне своей схемы они отличаются в зависимости от того, находится ли состояние линии бит или линии слов в верхнем или в нижнем уровне. Во флэш NAND связь между битовой линией и строкой слов напоминает вентиль NAND; во флэш NOR он напоминает вентиль NOR.

Флэш память было предложена Toshiba в 1980 году и основывалась на технологии EEPROM. Toshiba вывела флэш память на рынок в 1987 году. EEPROM нуждается в полном удалении перед тем как её можно перезаписать. Однако, флэш память NAND можно стирать, записывать и считывать блоками (или страницами), которые обычно намного меньше всего устройства. Флэш память NOR позволяет записывать в стираемое место одно машинное слова или считывать его независимо. Устройство флэш памяти обычно состоит из одной или нескольких микросхем флэш памяти (каждая из которых содержит множество ячеек флэш памяти) совместно с отдельной микросхемой контроллера флэш памяти.

Тип флэш памяти NAND в основном встречается в картах памяти, USB- накопителях, твердотельных накопителях (выпускаемых начиная с 2009 года), мобильных телефонах, смартфонах и аналогичных продуктах общего хранения и передачи данных. Флэш память NAND или NOR также часто применяется для хранения данных конфигурации в многочисленной цифровой продукции, та задача, которая ранее стала возможной благодаря EEPROM или статической RAM с питанием от батарейки. Ключевым недостатком флэш памяти является то, что она способна выдерживать относительно небольшое число циклов записи в каждом конкретном блоке [2].

Флэш память применяется в компьютерах, КПК, цифровых аудиоплеерах, цифровых камерах, мобильных телефонах, синтезаторах, научных приборах, промышленной робототехнике и медицинской электронике. Флэш память обладает быстрым временем доступа на чтение, но не столь быстрым как у статической памяти или у ПЗУ (ROM). В портативных устройствах она предпочтительнее дисков по причине своей устойчивости к механическим ударам.

Термин энергонезависимая память (NVM, Non-Volatile Memory) применяется для обозначения любого запоминающего устройства, способного сохранять состояние при отсутствии энергии [22]. NVM обеспечивают производительность, сопоставимую с современной DRAM (динамической оперативной памятью) и, как и к DRAM, к ним можно обращаться произвольно при небольшом снижении производительности. Однако, в отличие от DRAM, NVM остаются неизменными, что означает, что при отключении питания они не теряют данные. Таким образом, технологии NVM сочетают в себе преимущества как памяти (DRAM), так и хранилища (HDD - жёстких дисков, SDD - твердотельных дисков).

NVM представляют большое число характеристик, которые превращают их в существенно отличающиеся от HDD. Таким образом, работа с хранилищами данных в NVM может получать преимущества от использования иных подходов и методов, которые не поддерживают системы, спроектированные для работы с HDD. Более того, насколько нам известно, с момента появления флэш памяти NAND было предложено применением NVM в качестве единого уровня памяти, объединяющего концепции наших дней основной памяти и резервного хранилища [22] с целью замены всей иерархии памяти. Безусловно, такие изменения в архитектуре компьютера означают огромный сдвиг в разработке программного обеспечения (ПО), поскольку большинство приложений и операционных систем предназначены для хранения постоянных данных в виде файлов во вторичной памяти и обмена этими данными между уровнями с более быстрой, но энергонезависимой памятью.

Несмотря на то, что все работающие при такой архитектуре системы неизбежно выиграют от перехода с диска на NVM, одно из первых мест, на которое следует обратить внимание ри рассмотрении этого аппаратного совершенствования это система управления базами данных.

Хотя такие новейшие технологии NVM обладают большим числом общих характеристик, таких как низкая задержка, байтовая адресация и энергонезависимость, у них имеются некоторые ключевые различия. Такие отличия напрямую влияют на фундаментальные показатели, такие как задержка, плотность, длительность хранения и даже число хранимых в одной ячейке бит.

Наиболее распространённые технологии NVM включают [22]:

-

Флэш память

-

Магниторезистивная оперативная память

-

Оперативной памяти вращающего момента с передачей спина

-

Оперативной памяти с фазовым переходом (PCRAM, PRAM или PCM)

-

Резистивная оперативная память (RRAM, ReRAM)

Магнитные диски это набор жёстких пластин, покрытых ферромагнитным записывающим материалом. Диски представляют самый верхний уровень; однако это самая медленная технология.

Магнитные диски организованы следующим образом [4]:

-

Каждая поверхность подразделяется на концентрические окружности, носящие названия треков (дорожек).

-

Каждый трек делится на содержащие информацию секторы.

-

Обычно секторы хранят от 512 до 4096 байт.

Для их считывания или записи некая электромагнитная катушка помещается на передвигающийся кронштейн непосредственно между поверхностями этих пластин. Для доступа к содержащимся в нём данным сам диск обязан выполнять следующие три шага:

-

Позиционирование (seek): перемещение кронштейна на соответствующий трек.

-

Задержка вращения: Дождаться желательного сектора в его вращении под головку.

-

{Прим. пер.: в современных дисках с большим объёмом хранимых данных головка за один цикл пишет на трек сразу множество блоков (черепичный метод записи), что вносит некоторые коррективы в технологии действенной обработки внесения изменений, по своей сути схожие с внесением изменений во флэш память, например, смотри наш перевод материалов по Зонированным блочным устройствам.}

Рисунок 1.4 приводит сопоставление между различными обсуждавшимися выше имеющимися технологиями памяти. Основными отличиями выступают их ёмкости хранения и их времена доступа на выполнение операций ввода/ вывода для отдельного бита.

Несмотря на то, что память превращается в новый диск [21], непостоянство DRAM приводит к тому, что диски по- прежнему необходимы для резервного копирования данных. Передача данных между оперативной памятью и дисками осуществляется в единицах страниц, что, с одной стороны, сводит к минимуму вызываемое высокой задержкой позиционирования диска снижение производительности. Как правило, страница кратна секторам диска, которые выступают минимальной единицей обмена с диском. В современных архитектурах ОС обычно хранят буфер, который является частью основной памяти для ускорения взаимодействия между памятью и диском. Буфер в основном применяется для устранения промежутка в производительности между ЦПУ и диском. Это увеличивает производительность дискового ввода/ вывода за счёт буферизации операций записи для исключения дорогостоящего времени позиционирования диска при каждой операции записи и для буферизации операций считывания для быстрого ответа на последующие операции считывания тех же данных. В некотором смысле такой буфер относится к диску в точности так же как кэш к памяти. Кроме того, он раскрывает как пространственную, так и временную локализацию, что является важным фактором действенной обработки дискового ввода/ вывода.

Доступ к неоднородной памяти (NUMA, Non-uniform memory access) это архитектура самой подсистемы основной памяти, в которой значение задержек операций с памятью зависят от относительного положения соответствующего процессора, который и выполняет операции с памятью. Говоря шире, каждый процессор в некой системе NUMA обладает локальной памятью, доступ к которой может выполняться с минимальной задержкой, однако также способен выполнять по крайней мере ещё к одной удалённой памяти с более длительной задержкой.

Основной причиной применения архитектуры NUMA выступает улучшение полосы пропускания основной памяти и размер общей памяти целиком, который может быть развёрнут в неком узле сервера. NUMA позволяет делить на кластеры различные контроллеры памяти в отдельном узле сервера, создавая различные области памяти. Хотя системы NUMA и были развёрнуты в далёкие 1980е в специализированных системах [185], начиная с 2008 года все процессоры Intel и AMD содержат по одному контроллеру памяти. Таким образом, большинство современных многопроцессорных систем относятся к NUMA; поэтому осведомлённость о NUMA становится задачей основного направления.

В контексте систем управления данными, текущие направления исследований в области применения NUMA по- крупному можно разделить на три категории [21]:

-

разбиение данных таким образом, чтобы доступ к памяти для удалённых областей NUMA был минимальным.

-

управление воздействием NUMA на чувствительные к задержкам рабочие нагрузки, например, на транзакции OLTP.

-

действенное перемешивание данных по областям NUMA.